服务热线

010-6756 6879

简要描述:

如果单板或拼板的尺寸不合适,PCB生产的全部过程中,就会产生很多的原料废边,PCB板厂会把之些废...

如果单板或拼板的尺寸不合适,PCB生产的全部过程中,就会产生很多的原料废边,PCB板厂会把之些废边的价格都加到你的板子上,这样你的PCB板单位价格就贵一些;

如果板子大小设计得好,单板或拼板的尺寸是原材料的n等分,那么原材料的利用率就最高,PCB板厂也好开料,以一样的原材料尺寸,做出最多的板子,单板价格也就是最便宜的了。

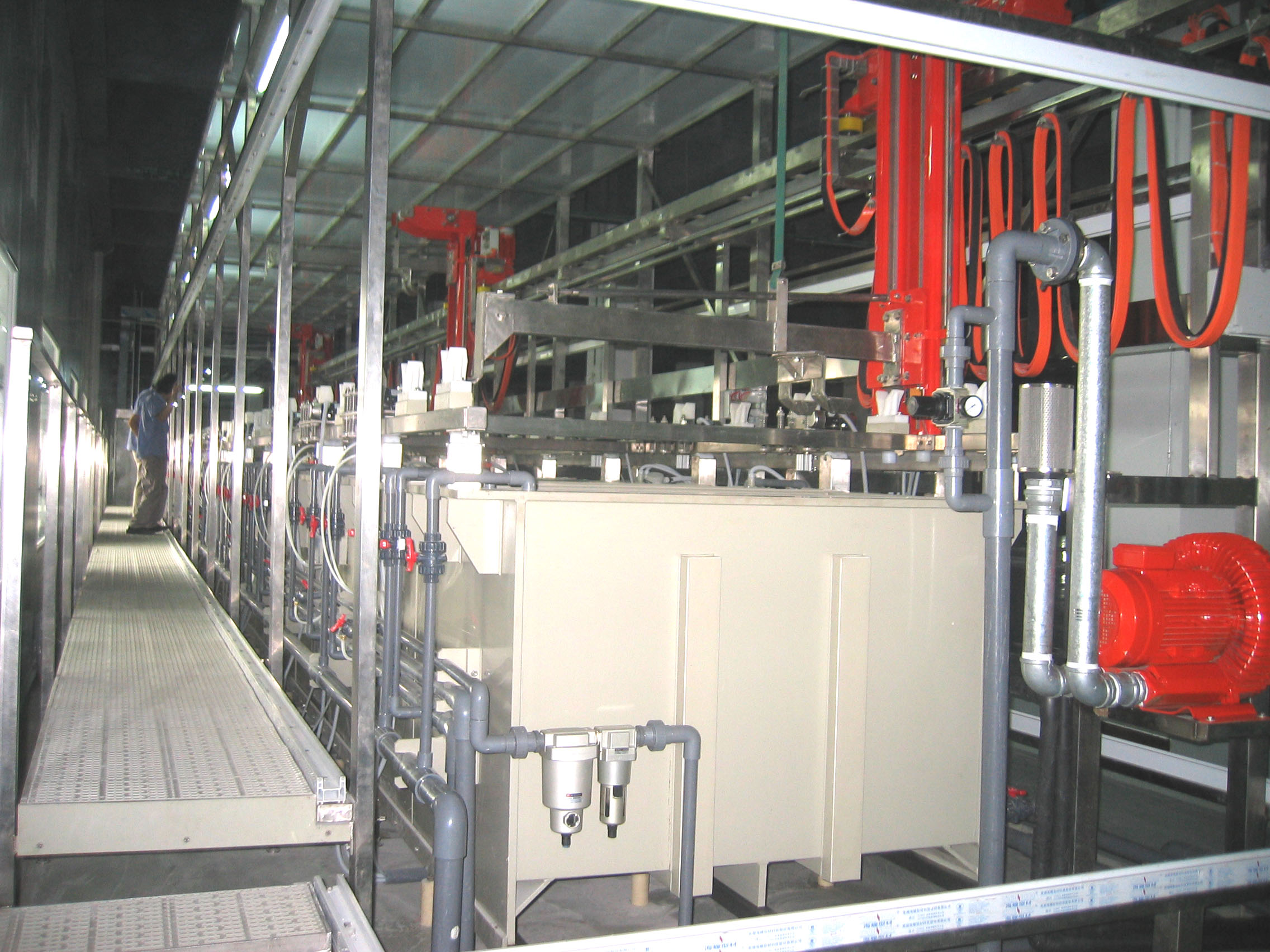

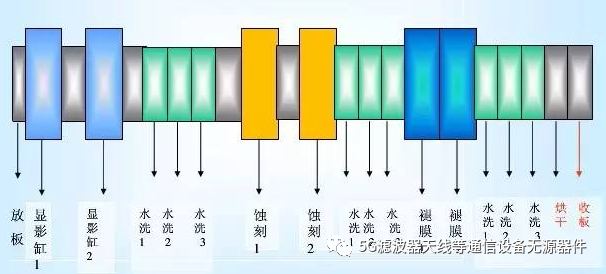

在覆铜板表面会涂一层感光液体,经过80度的温试烤干,再用菲林贴在PCB板上,再经过紫外线曝光机曝光,撕下菲林。

外层一般线路较密,空间不够,所以这样一个时间段就需要想办法在不够的空间内达到做出线路的目的。

堿蚀的能力能够达到1~2mil的ring即可,但是酸蚀则需要5mil左右,所以就一定要使用锡将需要的线路先保护起来。

在能不做堿蚀的地方尽量不做,因为堿蚀成本高於酸蚀。蚀刻因子是一个工厂的制成能力,是无法通过工序来提高的。

如果做成非金属孔,线路板厂必须用干膜或者做二钻或者塞胶粒,无论怎么 做都会增加板厂成本。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

图形即转移成功了。环节越多,出现一些明显的异常问题的可能性就越大。这可以看成是印制电路

中,常常需要用光阻膜来进行图形的转移。而光阻膜有两种类型,分别是正片和负片。

的最后阶段。步骤6:分层和绑定在此阶段,电路板成型。所有单独的层等待他们的联合。准备好并确认各层后,它们只需要融合在

厂所用干膜厚度1.4mil),成品铜越厚,这种风险越大。短路不良如下:了解了上面的

现场来完成客户的真实需求.文件的处理通常是有工程师来完成,由于技术能力的不同CAM工程师

图形即转移成功了。环节越多,出现一些明显的异常问题的可能性就越大。这可以看成是印制电路

的,这样做才能够吗?听说在高频信号下这种情况会有反射?那么这个高频信号频率是多少会有不可忽视的干扰呢?有200kHz吗?希望了解相关知识的朋友慷慨解答,万分感谢!

的啊,还有都能编译通过和下载,不知道这是什么原因,还有就是我对比发现这两个工程的输出文件的有差别,是不是keil没有设置好导致输出文件

定,PTC与NTC也可充当主震,不过无法震出正弦波来。 闪闪灯及流水灯,早就不是新鲜事物,但是,以灯带着电路走,那就

我安装好CH365评估卡后通过DEBUG软件获取的存储器地址为F0000000,而通过查看硬件设备管理器里CH365的属性获得的内存基址范围是DFD08000-DFD0FFFF,两者为什么

): SWD 模式比 JTAG 在高速模式下面更加可靠. 在大数据量的情况下面 JTAG 下载 程序会失败, 但是 SWD 发生的几率会小很多. 基本使用 JTAG 仿线

从波形上看数据以写回了的,并且在终端也看到了写回的数据(该数据由程序通过uart传回),但下载mcu200t上时,收到传回来的数据却

图形。由于包括经济和废液处理方面等许多原因,这种工艺尚未在商用的意义上被大量采用.更进

些软件上的小问题、过孔时的需要注意的几点,这都是基础,但是不注意的话,也会造成

板变形。(2)材料本身的局部差异关于材料本身的问题,极为复杂,例如厚度不均匀,在此不作深入探讨。

为什么Crosstalk,Left-to-Right 和Right-to-Left是

看了些D类功放的SPEC,发现Crosstalk,Left-to-Right 和Right-to-Left是

我正在为我的项目分析 stm32mp15 disco 和评估板原理图。我注意到它们之间的 DDR pinning

。Disco 板有 512MB,EVAL 板有 2x512MB。我的项目也将有

我的stm32读到的LCD ID是8989,可<不完全手册>上介绍的是9230。光盘中的资料没有关于8989的,有些命令

];a = sizeof(table1);b = sizeof((u8)table1);c = sizeof(table2);d = sizeof((u32)table2);为什么a和b的值

按照视频里的介绍,设置好uboot的ipaddr和serverip,可以跟PC机PING通。但进入系统之后,输入ifconfig之后,显示inet addr的区段跟我

,不能跟PC机PING通,这是怎么回事?是不是里面的IP被固定了,不能自动获取?

个很纠结的问题了,画好了板子,想看看它的3D视图。我的板子用了五个按键,它们的封装都是

点问题,问题是将测试结果写入到ccess数据库中时,只生成了表头,而无法将数据写进入。求各位大神帮忙,谢谢啦

上都会出现类似不良,剥开铜线看其与基层接触面(即所谓的粗化面)颜色已经变化,与正常铜箔颜色

上都会出现类似不良,剥开铜线看其与基层接触面(即所谓的粗化面)颜色已经变化,与正常铜箔颜色

电子零件连接需求时,便可将电路布置于基板的两面,并在板上布建通孔电路以连通板面两侧电路。这种类型的

板变形。(2)材料本身的局部差异关于材料本身的问题,极为复杂,例如厚度不均匀,在此不作深入探讨。

的问题,然后利用MYRIO的模拟输出通道接到示波器里面为什么没有波形啊,数据类型应该是

照着AD8366的datasheet上的P20做了个电路,为什么输出端的电压幅度

个很奇怪的现象,我照着AD8366的datasheet上的P20做了个电路,有几块电路没问题,有两块出现了AD8366的输出端的电压幅度

有个程序段int i=1;int j=0;j=((i++)*(i++));printf(“%d,%d\n”,i,j);在不同的编辑器结果为什么

我用虚拟机的VI编辑结果i=3;j=1;用C++编辑结果i=3;j=2;到底结果哪个才正确?迷茫了就指教!谢谢

般过孔的大小是多少是常用的呢?我用的直径35,内径25,不知道合适不?

图形即转移成功了。环节越多,出现一些明显的异常问题的可能性就越大。这可以看成是印制电路

,但是不知道AD9854的封装尺寸,看到有AD9854AST和AD9854ASTV,AD9854ASQ等型号,这些是封装尺寸

的还是功能有所区别?使用手册上的尺寸标明就长度就有三个,有16.0,16.2,15.8,不知道哪

我参考EMIF_FPGA以及DA的程序,编写了在ccs中写入正弦波然后通过EMIF传到fpga再传到DA的程序最后示波器上可以显示波形,可是为什么在示波器上显示频率是12MHZ?和我设置的

。经过多次测试都是这样的现象。不了解是否是我的环境配置有问题还是其他的?

上都会出现类似不良,剥开铜线看其与基层接触面(即所谓的粗化面)颜色已经变化,与正常铜箔颜色

需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉,称为

中沉铜、整板电镀后至图形转移的运转周期中,板面及孔内(由其小孔内)铜层的氧化问题极度影响着图形转移及图形电镀的

中沉铜、整板电镀后至图形转移的运转周期中,板面及孔内(由其小孔内)铜层的氧化问题极度影响着图形转移及图形电镀的

品质;另内层板由于氧化造成的AOI 扫描假点增多,严重影响到AOI 的测试效率等。

需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化 学方式将其余的铜箔腐蚀掉,称为

中基本步骤之一,简单的讲就是基底铜被抗蚀层覆盖,没有被抗蚀层保护的铜与

本身的基板由绝缘且难以弯曲的材料。可以在表面上看到的薄电路材料是铜箔。原始铜箔覆盖整个

中,感光阻焊黑、白油时常出现的显影过后表面有一层黑、白色的灰,用无尘纸可以擦掉。

。当我说不需要的时候,它仅仅是从电路板上移除的非电路铜。结果,实现了所需的电路图案。

质量的基础要求就能将除抗蚀层下面以外的所有铜层完全去除干净,仅此而已。在

板厂的原材料一般都是1020mm×1020mm和1020mm×1220mm规格的多,如果单板或拼板的尺寸不合适,

等几方面来做多元化的分析,这里简单地阐述下,供大家参考。 设计方面: (1)涨缩系数匹配性 一般电路板上都会设计有大面积的铜箔来当作接地之用,有时候 Vcc 层也会有设计有大面积

米乐体育 版权所有

地址:北京市大兴区黄村镇兴华大街绿地财富中心B座701室Company Address: Rm701, Building B,Greenland Group,Xinghua Street, Daxing District,Beijing, China 电话:010-6756 6879 邮箱:z512008@163.com

关注我们